Transforming EDA with AI: A Leap Forward

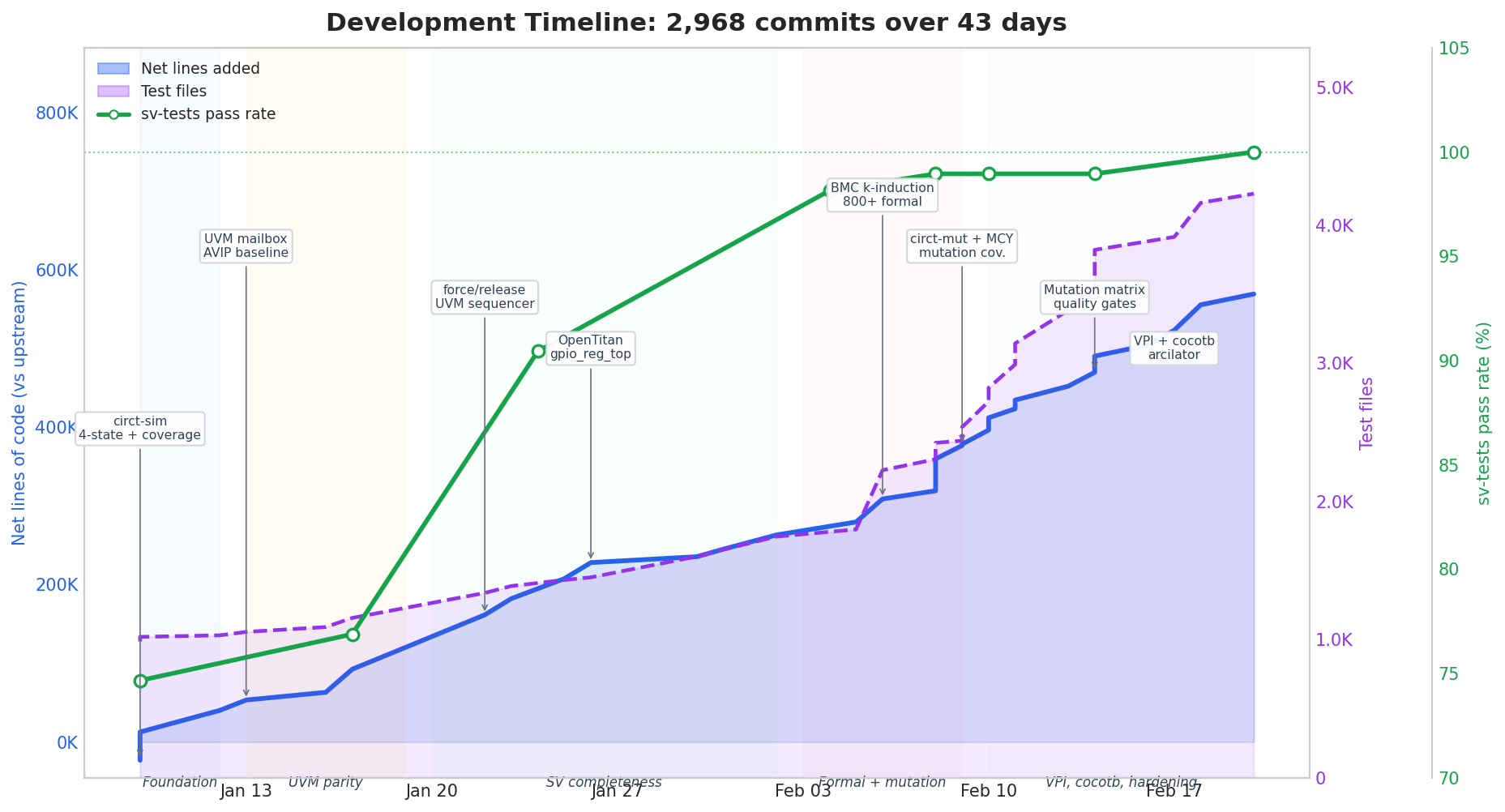

In an innovative journey, a Normal engineer harnessed the power of AI to craft a practical verification stack atop CIRCT, revolutionizing hardware design. Over 43 days, 2,968 commits enriched the open-source landscape with:

- AI-Powered Contributions: Event-driven simulator, VPI/cocotb integration, and UVM runtime support.

- Complexity Simplified: Bridged the gap from Verilog parsing to actual simulation, aiding real-world testbenches.

- Massive Growth: Added 580,430 lines across 3,846 files, representing substantial progress toward IEEE compliance.

Key achievements include:

- Formal Verification: Over 1,000 commits focused on enhancing verification capabilities.

- Real-World Testing: Successfully ran various testbenches, confirming the simulator’s robustness.

The Future of EDA

This project showcases that a single engineer, empowered by AI, can tackle complex verification in weeks rather than years, challenging traditional industry norms.

🔗 Curious about breaking barriers in tech with AI? Dive into the full tale here and share your thoughts!